## Bringing Parallel Patterns out of the Corner: the P<sup>3</sup>ARSEC Benchmark Suite

Daniele De Sensi, Tiziano De Matteis, Massimo Torquati, Gabriele Mencagli, Marco Danelutto

University of Pisa, Department of Computer Science

## **Parallel Patterns:**

high-level abstractions solving recurrent problems

Prove that few parallel patterns can model

many real applications

Implementation with FastFlow and SkePU2 publicly available

Comparison between: Pthreads

OmpSs

FastFlow

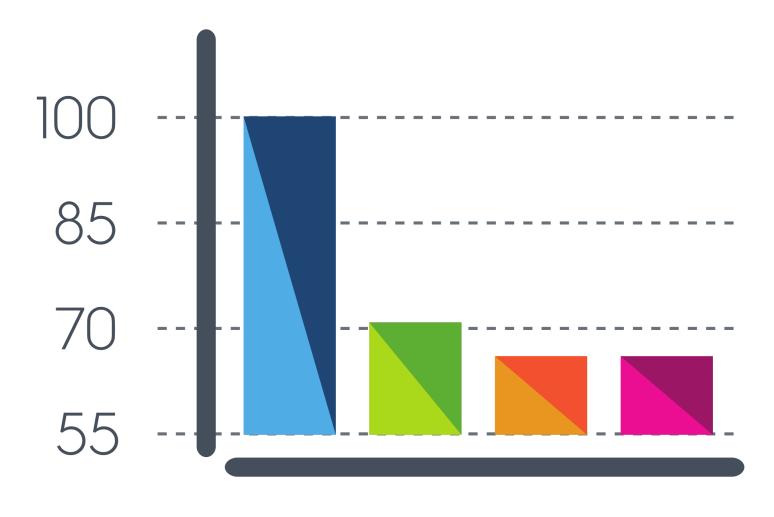

Lower programming effort thanks to high-level abstraction (up to -87% LOC with respect to Pthreads)

Lines of Code (Lower = Better)

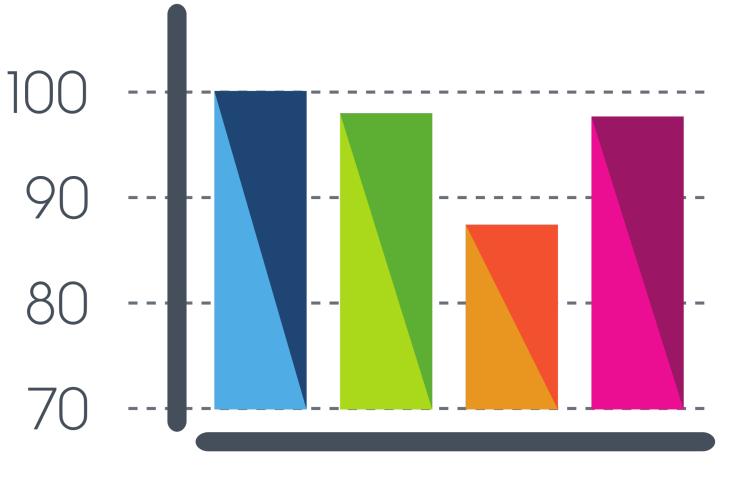

**Execution Time** (Lower = Better)

Improved performance thanks to a simpler design (up to +42% faster than Pthreads)

## Ferret Speedup w.r.t. Sequential

| Alt. 1 | Alt. 2 | Alt. 3 | Alt. 4 |

|--------|--------|--------|--------|

| 51.13  | 52.9   | 55.69  | 92.6   |

D. De Sensi, T. De Matteis, M. Torquati, G. Mencagli and M. Danelutto, "Bringing Parallel Patterns out of the corner: the P<sup>3</sup>ARSEC Benchmark Suite"

In ACM Transactions on Architecture and Code Optimization

**Detailed results** on: Intel Xeon Server, Intel Xeon Phi KNL, IBM Power8

Additional comparison with TBB and OpenMP

http://calvados.di.unipi.it/paragroup/

paragroup@di.unipi.it